Very Large Scale Integration System on Chip Design (VLSI SoC) plays a pivotal role in the semiconductor industry. As the demand for more advanced, powerful, and energy-efficient devices continues to rise, the need for skilled professionals in VLSI SoC design also increases. The industry requires engineers who can effectively design, verify, and optimize complex integrated circuits and systems that serve as the foundation for modern electronic devices. SoC Design integrate a wide range of functions, including processors, memory, and communication interfaces, into a single system, delivering significant benefits in terms of performance, power efficiency, size, and cost.

| Program Type | Program | Program Start Date | Program Duration | Admission Link |

|---|---|---|---|---|

| Job Oriented Skill Enhancement Program | ASIC RTL Design Verification | June 16th, 2025 | 6 to 8 Months | Know More |

| Job Oriented Skill Enhancement Program | Physical Design (RTL to GDSII) | June 16th, 2025 | 6 to 8 Months | Know More |

| Job Oriented Skill Enhancement Program | Analog Layout | June 16th, 2025 | 6 to 8 Months | Know More |

| Skill Enhancement & Internship | ASIC Emulation on FPGA | Feb 4th, 2025 | 4 Months | Download Brochure Enroll Now |

| Job Oriented Goodwill Program | VLSI SOC Design | Oct 16th, 2024 | 4 Months (Ongoing) |

Know More |

ASIC Emulation on FPGA

Skill Enhancement & Internship

4 Months | Classroom

Starts on: Feb 4th, 2025

ASIC RTL Design Verification

Job Oriented Skill Enhancement Program

6-8 Months | Classroom

Starts on: June 16th, 2025

Physical Design (RTL to GDSII)

Job Oriented Skill Enhancement Program

6 to 8 Months | Classroom

Starts on:June 16th, 2025

.jpg)

Analog Layout

Job Oriented Skill Enhancement Program

6 to 8 Months | Classroom

Starts on: June 16th, 2025

VLSI SOC Design

GOODWILL PROGRAM

4 Months | Classroom

Started on Oct 16th, 2024

Start Date: Feb 4th, 2025

Duration: 4 Months

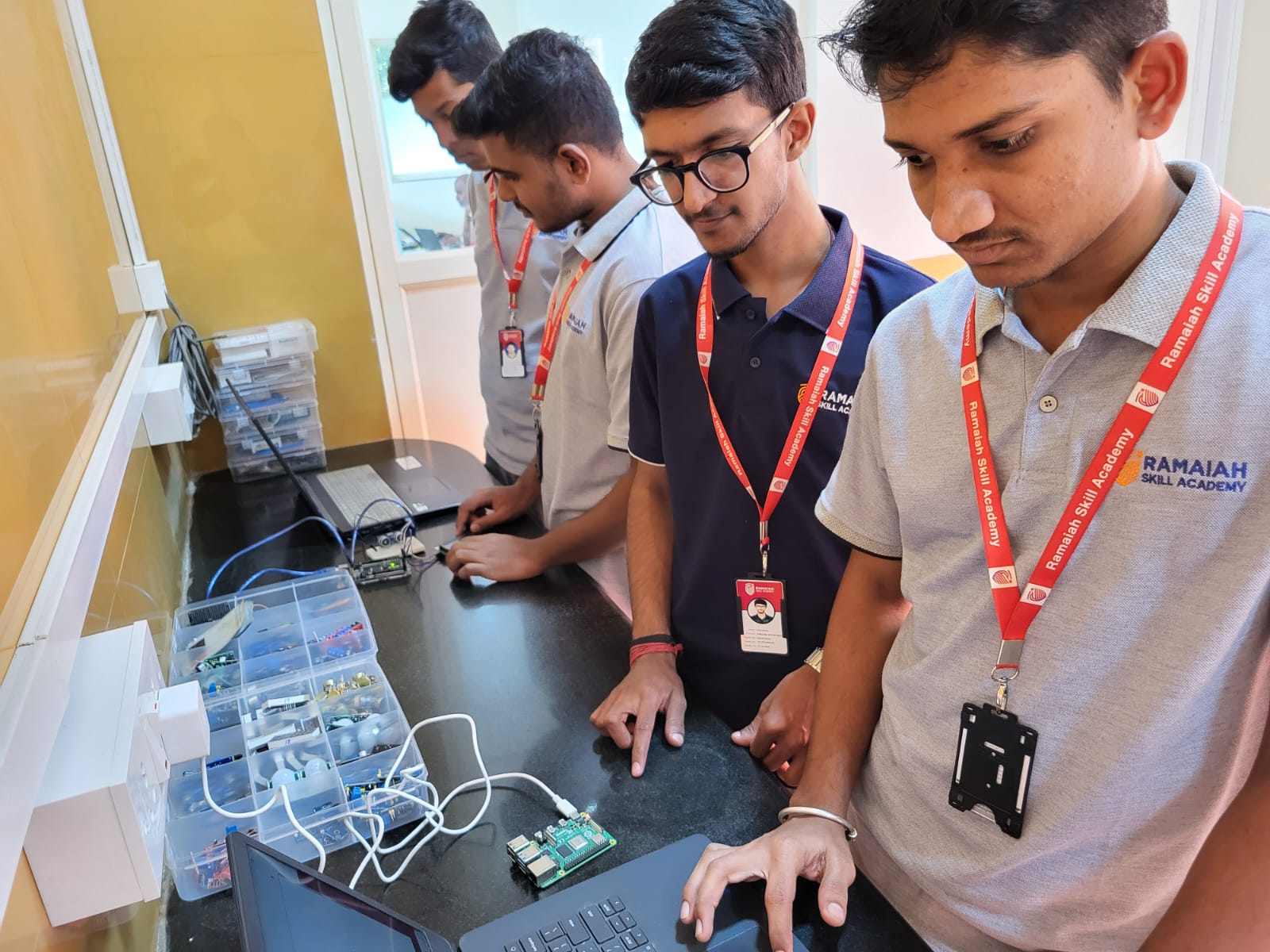

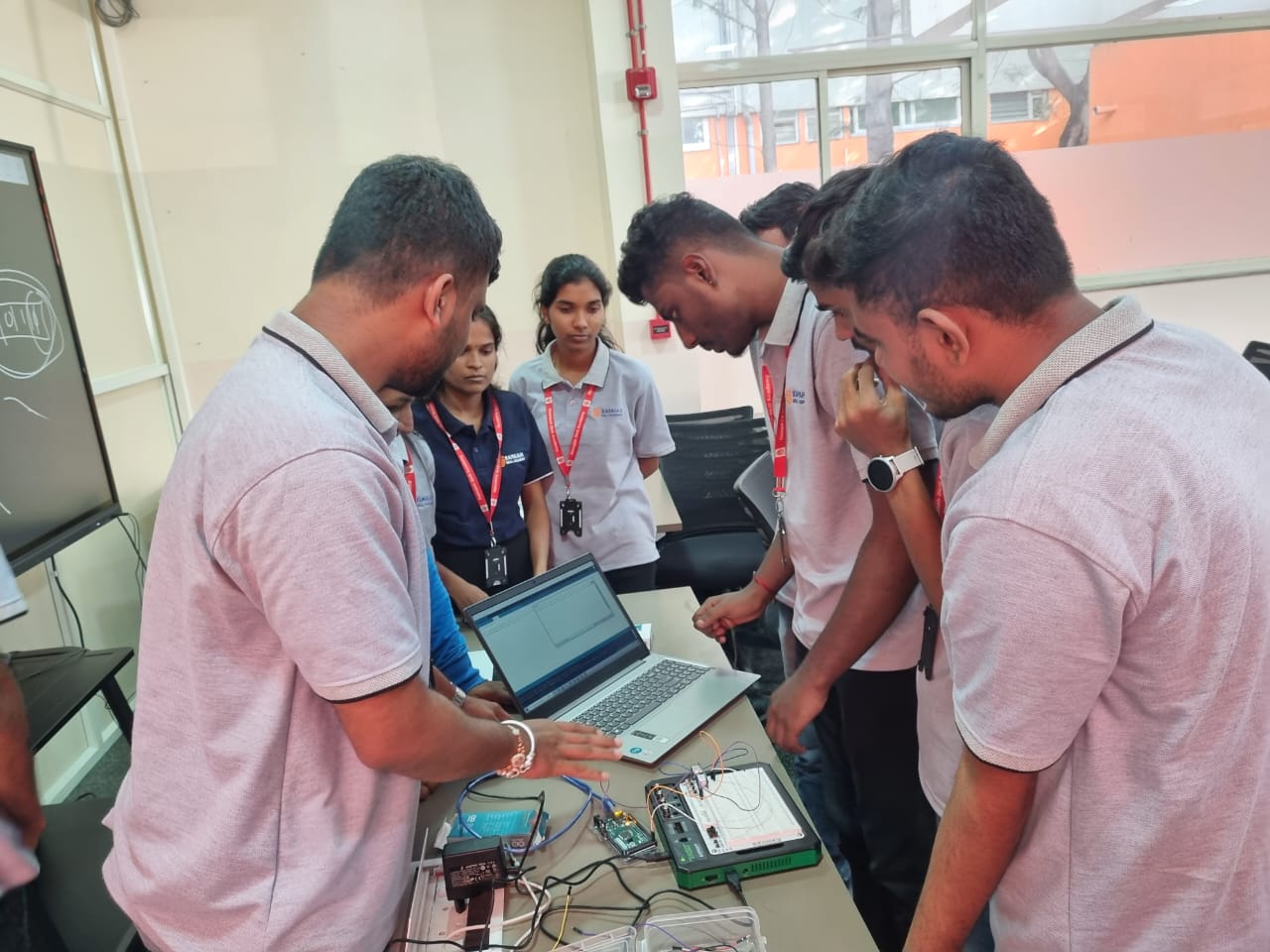

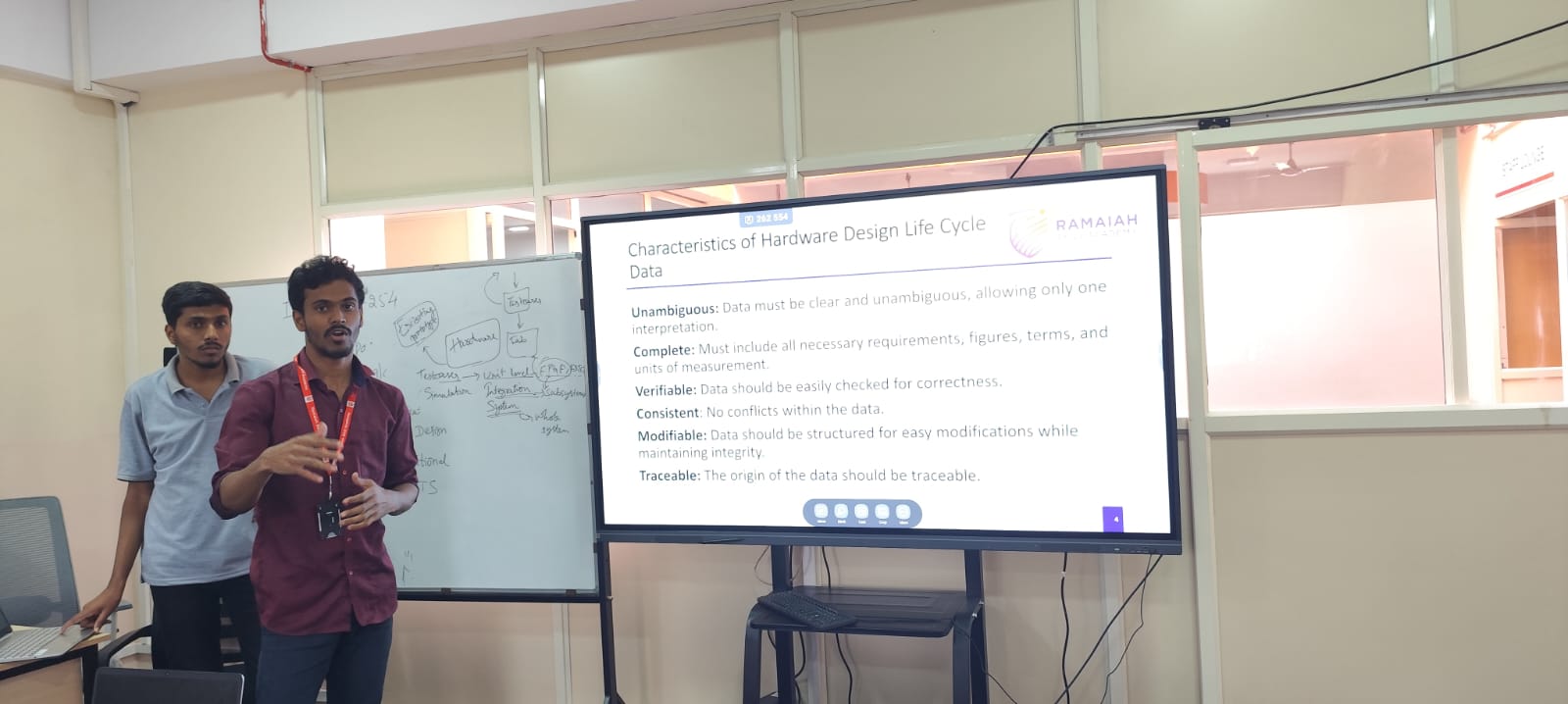

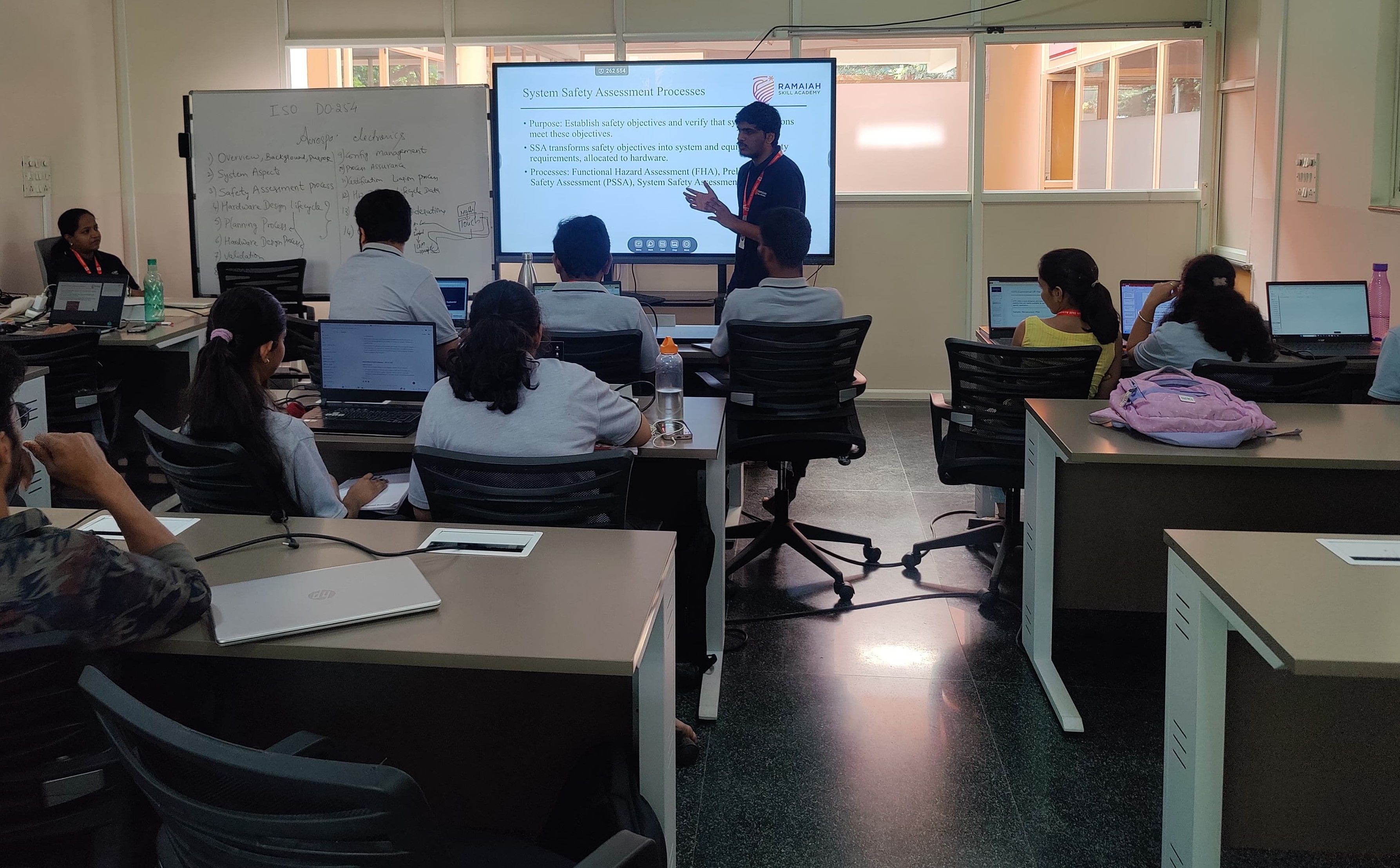

The ASIC Emulation on FPGA course covers the design, verification, and emulation of Application-Specific Integrated Circuits (ASICs) using Field-Programmable Gate Arrays (FPGAs). This course is ideal for students and professionals in VLSI design, semiconductor engineering, embedded systems, and hardware verification. The course offers a comprehensive exploration of the techniques and tools involved in emulating ASIC designs on FPGA platforms. Students will learn how to convert an ASIC design into a format compatible with FPGAs, perform emulation and testing, and validate the design in a hardware environment. The focus will be on both the theoretical and practical aspects of ASIC emulation, FPGA synthesis, verification, and debugging. At the end of the course, students will present their hands-on projects, detailing the challenges encountered, solutions implemented, and lessons learned throughout the process.

ASIC Design Verification using SystemVerilog and Universal Verification Methodology (UVM) provides a powerful, scalable, and efficient framework for verifying complex ASIC RTL Designs. This Program provides an in-depth understanding of ASIC design verification using SystemVerilog and UVM. Trainees will learn the key concepts, methodologies, and tools needed to verify the functionality of ASIC designs effectively. The program covers essential topics, including creating robust testbenches, functional verification using assertions, constrained random testing, and integrating the UVM framework to structure and scale verification environments. By the end of this program, students will be equipped with the skills to perform advanced verification of ASIC designs, ensuring that the designs meet specifications and are free from functional errors before moving to physical implementation.

The physical design of a VLSI chip refers to the steps that are involved in transforming a high-level design (usually represented in Register Transfer Level (RTL)) or netlist form) into a physical layout that can be fabricated on a semiconductor wafer. The physical design process is a critical part of the overall VLSI design flow and directly impacts the chip’s performance, power consumption, and size (often referred to as PPA: Power, Performance, and Area). The Physical Design (RTL to GDSII) Program offers a comprehensive and hands-on approach to understanding the ASIC design flow from RTL to GDSII. Trainees will gain practical experience with the physical design tools used in the industry and will be prepared to optimize designs for power, performance, and area while ensuring that the final design meets all manufacturing requirements.

Analog layout refers to the physical design process for analog circuits in Very Large Scale Integration (VLSI). Unlike digital designs, which use standard cells (pre-designed and optimized logic gates), analog designs are custom specific, meaning the layout of each circuit element, such as transistors, capacitors, and resistors, must be manually placed and routed. The layout of analog circuits requires a careful balance between electrical performance, manufacturability, and physical constraints. The Analog Layout Program provides students and professionals with the critical skills and knowledge required to design high-performance analog circuits at the physical level. With a focus on layout techniques, parasitic management, and design verification, this Program prepares participants to work with the tools and methodologies used in modern VLSI analog design. Whether one is aiming for a career in analog IC design or enhancing one's existing skills, this Program offers the foundation needed for success in the industry.